江之行,来自山东省枣庄市,本科毕业于西安电子科技大学,现为清华大学集成电路学院2022级直博生。

工欲善其事,必先利其器

江之行从大四起加入课题组,在导师唐建石的指导下,开始对忆阻器器件的编程与可靠性优化的深入探索。通过两年多的钻研和实践,江之行深刻认识到实验准备工作的重要性。他坚信,高效的前期准备是科研成功的关键,特别是在正式实验中频繁使用的模块,深度优化可以极大提升后续实验的效率。

与导师唐建石老师以及课题组其他同学在教师节的合影

由于单个忆阻器器件性能差别很大,对编程和可靠性优化的研究需要对阵列数据进行统计分析,于是,江之行投入大量的精力进行测试工作与大规模的数据分析。初入研究团队时,他发现组里现有的1K测试平台效率不足,难以满足大规模测试的需求。通过钻研测试机手册,并对测试中最底层的模块逐一优化,他成功将系统测试效率提高了30倍。此外,他发现原先测试流程只能采集1ms至1s时间范围内的数据,限制了对长时间尺度下忆阻器性能的分析。为此,他创新性地设计了对数时间流水线测试方案,从而可根据实验需求实现1ms-1000s乃至更长时间尺度的测试数据采集,为揭示忆阻器编程与可靠性的规律提供了强有力的数据支持。

当在1K测试平台上取得初步成果后,导师唐建石鼓励江之行在更大规模的144K测试平台上验证他的编程算法。在熟悉144K平台的过程中,他发现目前芯片编程过程完全依赖于CPU端的Python代码执行,效率低下。于是,他自学了Vivado HLS开发工具链,并利用FPGA大幅加速编程过程。经过不懈努力,144K测试平台的编程效率提升了80倍,将原本需要10小时的编程任务缩短至不到8分钟,为后续的研究工作奠定了坚实的基础。

笃定前行,勇于创新

忆阻器编程与可靠性优化是领域内的重大挑战,江之行通过文献调研和测试,发现现有电导调控方案存在无法同时满足效率和可靠性的问题,这直接损害了模拟存算系统的性能。他通过大量的测试工作与大规模的数据分析,理清了电导调控过程中操作、时间、状态等基本操作元素对编程结果的影响及其内在原理。

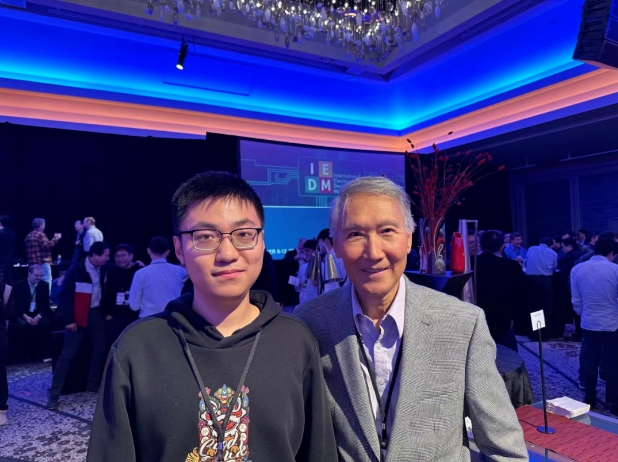

在IEDM会场与3D晶体管之父胡正明教授的合影

基于这些深入理解,他提出了创新的COPS编程方案,首次打破了忆阻器器件编程效率和稳定性不可兼得的困境。与传统方案相比,新的方案在相同编程效率下能使忆阻器的保持时间提升1000倍,并且在保证相同可靠性下编程效率提升60%。他的成果在144K存算一体计算系统上得到了验证,尤其是在对噪声敏感的去噪扩散概率模型(DDPM)任务中展现了卓越性能,在10000s后仍能保持3-4bit软件精度,其编程方案的各项指标均优于现有技术。最终,江之行以第一作者身份在集成电路器件领域顶级会议IEDM2023上发表了这项成果,并进行了口头报告。

结语

江之行深知,科研是一场没有终点的马拉松,需要的是持之以恒的努力和对知识的不懈追求。展望未来,他立志保持初心,不断在学术和科研上精进,作为集成电路学院的一员,他致力于“做有用的科研”,以实际行动为国家的芯片事业进步贡献自己的力量。